FX Core Instruction Set V1.0 Feb 2020

## Table of Contents

| ntroduction                                                                                                                                        | 6    |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Block Diagram                                                                                                                                      | 7    |

| Registers and Memory                                                                                                                               | 9    |

| FLAGS Register                                                                                                                                     | 10   |

| Instruction Format                                                                                                                                 | 10   |

| Nath Operations                                                                                                                                    | 13   |

| ABS – Absolute value of a core register                                                                                                            | 14   |

| CLRACC64 – Clear the 64-bit accumulator                                                                                                            | 14   |

| ADDI – Add a 16bit signed integer to 32 bit core register, not saturated (modulo 2 <sup>32</sup> )                                                 | 14   |

| ADD – Unsigned addition of two core registers, not saturated (modulo 2 <sup>32</sup> )                                                             | 14   |

| ADDS – Signed addition of two core registers, saturated                                                                                            | 14   |

| ADDSI – Signed addition of 32-bit S.31 core register with 16-bit S.15 (MSB aligned), saturated                                                     | 15   |

| SUB – Unsigned subtraction of two core registers, not saturated (modulo 2 <sup>32</sup> )                                                          | 15   |

| SUBS – Signed subtraction of two core registers, saturated                                                                                         | .15  |

| SL – Shift left logical using an immediate 5-bit value                                                                                             | 16   |

| SLR – Shift left logical using the 5-LSBs of a core register                                                                                       | 16   |

| SLS – Shift left arithmetic with saturation using an immediate 5-bit value                                                                         | 16   |

| SLSR – Shift left arithmetic with saturation using the 5-LSBs of a core register                                                                   | 16   |

| SR – Shift right logical using an immediate 5-bit value                                                                                            | 17   |

| SRR – Shift right logical using the 5-LSBs of a core register                                                                                      | 17   |

| SRA – Shift right arithmetic using an immediate 5-bit value                                                                                        | .17  |

| SRAR – Shift right arithmetic using the 5-LSBs of a core register                                                                                  | 17   |

| MACRR – Multiply and accumulate using 64-bit accumulator (S.63), 32-bit (S.31) x 32-bit (S.31) multiply with saturation                            | . 18 |

| MACRI – Multiply and accumulate using 64-bit accumulator (S.63), 32-bit (S.31) x 16-bit (S.15) coefficient multiply                                | . 18 |

| MACRD – Multiply and accumulate using 64-bit accumulator (S.63), 32-bit (S.31) x 16-bit (S.15) delarmemory multiply                                |      |

| MACID – Multiply and accumulate using 64-bit accumulator (S.63), 8-bit (S.7) coefficient multiply x 1 bit (S.15) delay memory                      |      |

| MACHRR – Multiply and accumulate using 64-bit accumulator (S3.60), 32-bit (S.31) x 32-bit (S.31 shifted to S3.28) multiply                         | . 19 |

| MACHRI – Multiply and accumulate using 64-bit accumulator (S3.60), 32-bit (S.31) x 16-bit (S.15 shifted right and zero appended to S3.28) multiply | . 19 |

|      | ACHRD – Multiply and accumulate using 64-bit accumulator (S3.60), 32-bit (S.31) x 16-bit (S.15                                                                                               |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | ifted right to S3.15 and zero appended to S3.28) delay memory                                                                                                                                | 20 |

|      | ACHID – Multiply and accumulate using 64-bit accumulator (S3.60), 8-bit (S.7 zero appended to 32) coefficient x 16-bit (S.15 shifted right to S3.15 and zero appended to S3.28) delay memory |    |

|      | ultiply                                                                                                                                                                                      | 20 |

|      | ULTRR – Saturated multiply of two core registers, 32-bit (S.31) x 32-bit (S.31), 32 MSBs of the 64-broduct in ACC32                                                                          |    |

| M    | ULTRI – Multiply to 32-bit accumulator (S.31), 32-bit (S.31) x 16-bit (S.15) multiply                                                                                                        | 21 |

| NE   | EG – Negate a core register, 2's complement saturated                                                                                                                                        | 21 |

| LO   | OG2 – Calculate the log base 2 of the absolute value of a register                                                                                                                           | 21 |

| EX   | (P2 – Calculate 2^ value of a register                                                                                                                                                       | 21 |

| Сору | y Operations                                                                                                                                                                                 | 22 |

| СР   | PY_CC – Copy from one core register to another                                                                                                                                               | 23 |

| СР   | PY_CM – Copy from MREG register to core register                                                                                                                                             | 23 |

| СР   | PY_CS – Copy from special function register (SFR) to core register                                                                                                                           | 23 |

| СР   | PY_MC – Copy from core register to MREG register                                                                                                                                             | 23 |

| СР   | PY_SC – Copy from core register to special function register (SFR)                                                                                                                           | 24 |

|      | PY_CMX – Copy from MREG register to core register using a second core register as the index gister to address the MREG                                                                       | 24 |

| Load | l/store Operations                                                                                                                                                                           | 25 |

| RD   | DACC64U – Copy the upper 32-bits from the 64-bit accumulator to a core register                                                                                                              | 26 |

| RD   | DACC64L – Copy the lower 32-bits from the 64-bit accumulator to a core register                                                                                                              | 26 |

| LD   | DACC64U – Load the upper 32-bits of the 64-bit accumulator from a core register                                                                                                              | 26 |

| LD   | DACC64L – Load the lower 32-bits of the 64-bit accumulator from a core register                                                                                                              | 26 |

| RD   | DDEL – Read from delay memory into a core register using an immediate address                                                                                                                | 26 |

| W    | RDEL – Write to delay memory from a core register using an immediate address                                                                                                                 | 27 |

|      | ODELX – Read from delay memory into a core register using a second core register as the index gister to address the delay memory                                                             | 27 |

|      | RDELX – Write the value in a core register to delay memory using a second core register as the dex register to address the delay memory                                                      | 27 |

|      | DDIRX – Read from delay memory into a core register using a second core register as the index gister to address the delay memory without adding address counter                              | 27 |

|      | RDIRX – Write the value in a core register to delay memory using a second core register as the ingister to address the delay memory without adding address counter                           |    |

|      | AT64 – Copy the 32 MSBs from ACC64 (S3.60), shift left 3 bits and saturate to an S.31 format and ace into core register                                                                      | 28 |

|    | WRDLD – Load a 16-bit immediate value to the upper 16-bits of a core register, 0s to LSBs | 28 |

|----|-------------------------------------------------------------------------------------------|----|

| Lc | ogic Operations                                                                           | 29 |

|    | INV – Invert (1's comp) core register                                                     | 30 |

|    | OR – Bitwise OR of 2 core registers to ACC32                                              | 30 |

|    | ORI – Bitwise OR of core register with a 16-bit immediate value 0 extended to ACC32       | 30 |

|    | AND – Bitwise AND of 2 core registers to ACC32                                            | 30 |

|    | ANDI – Bitwise AND of core register with a 16-bit immediate value 0 extended to ACC32     | 31 |

|    | XOR – Bitwise XOR of 2 core registers to ACC32                                            | 31 |

|    | XORI – Bitwise XOR of core register with a 16-bit immediate value 0 extended to ACC32     | 31 |

|    | JGEZ – Jump if core register value is >= 0                                                | 31 |

|    | JNEG – Jump if core register value is < 0                                                 | 32 |

|    | JNZ – Jump if core register value is != 0                                                 | 32 |

|    | JZ – Jump if core register value = 0                                                      | 32 |

|    | JZC – Jump if core register value is different sign from acc32                            | 32 |

|    | JMP – Jump always                                                                         | 33 |

| E> | ktended Operations                                                                        | 34 |

|    | APA – First instruction for all-pass filter with fixed values                             | 35 |

|    | APB – Second instruction for all-pass filter with fixed values                            | 35 |

|    | APRA – First instruction for all-pass filter using register for coefficient value         | 35 |

|    | APRB – Second instruction for all-pass filter using register for coefficient value        | 36 |

|    | APRRA – First instruction for all-pass filter using register for both values              | 36 |

|    | APRRB – Second instruction for all-pass filter using register for both values             | 36 |

|    | APMA – First instruction for all-pass filter using MREG for delay                         | 36 |

|    | APMB – Second instruction for all-pass filter using MREG for delay                        | 37 |

|    | CHR – Chorus on delay mem                                                                 | 37 |

|    | PITCH – Pitch shift on delay mem                                                          | 37 |

|    | SET – Set a user bit high or low using the selected bit of a register                     | 38 |

|    | INTERP – Do a linear interpolation between two samples in a delay line                    | 38 |

| R  | eserved Words                                                                             | 39 |

|    | Core Registers                                                                            | 40 |

|    | Non-core CPU Registers                                                                    | 40 |

|    | SRAM Based Registers                                                                      | 40 |

|    | Special Function Registers                                                                | 40 |

## FX Core Instruction Set Document Version 1.0 February 2020

| Other Reserved Words and their value                                               | 41 |

|------------------------------------------------------------------------------------|----|

| Assembler Directives                                                               | 44 |

| .EQU – Equate a name to a value                                                    | 45 |

| .RN – Rename a register                                                            | 45 |

| .MEM – Declare a memory block                                                      | 45 |

| .CREG – Set a core register to an initial value when program is loaded             | 45 |

| .MREG – Set a memory register to an initial value when program is loaded           | 46 |

| .SREG – Set a special function register to an initial value when program is loaded | 46 |

| .L – Use the lower 16-bits of a 32-bit word in an instruction (appended to value)  | 46 |

| .U – Use the upper 16-bits of a 32-bit word in an instruction (appended to value)  | 46 |

| Tap Tempo Operation                                                                | 47 |

| Memory Management                                                                  | 49 |

Introduction

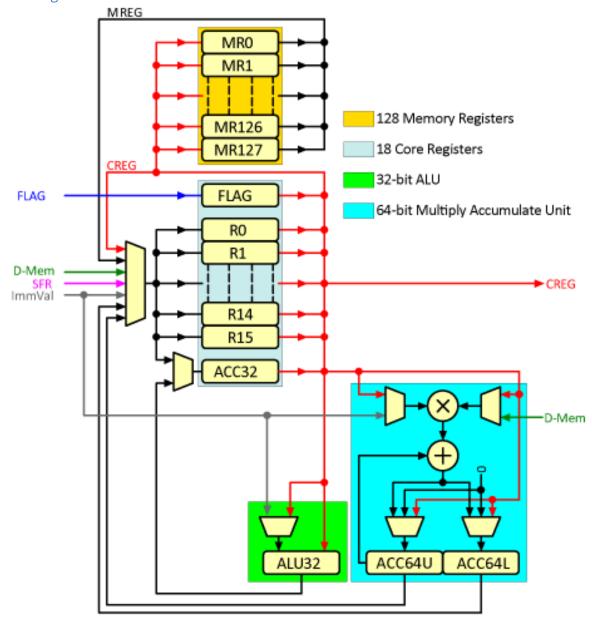

## Block Diagram

The FX Core has 3 sets of registers, 20 DSP/ALU registers (19 core and a "non-core" 64-bit accumulator ACC64), 128 32-bit MREG registers and special function registers (SFR). DSP/ALU registers are faster for the DSP/ALU to access and use.

The number of instructions that can be executed in a single sample period is dependent on the instructions used. Instructions take one or more clocks to execute so the total number of clocks a program takes depends on the mix of instructions. Programs have about 3500 clocks per sample period at 48KHz sample rate. There are more clocks available at lower sample rates.

The instruction RAM can hold 1024 instructions but the number of instructions that can be executed in a sample period depends on the mix of instructions and the sample rate the FXCore is being run at.

The FX Core assembler will estimate how many clocks have been used and warn the user when it exceeds 90% when the program is assembled.

The internal FLASH can hold 16 programs, when a program is selected the program is loaded into the instruction RAM and executed from there. Additionally each program has an associated header that will preload values into the core registers, MREG registers and some of the SFRs. This allows users to set initial values in their programs without wasting instructions.

On program change, while the instruction RAM is being loaded with the new program, the outputs are muted, the delay RAM is cleared and the initial values from the program headers are loaded into their target registers.

## Registers and Memory

DSP/ALU core registers are 32-bit and are called R0 to R15, ACC32 and FLAGS. While ACC64 resides in the core of the chip it is not part of the core register bank and is not considered a core register.

| Name  | Encoding | Туре | Remark             |

|-------|----------|------|--------------------|

| R0    | 00000    | R/W  | General use        |

| R1    | 00001    | R/W  | General use        |

| R2    | 00010    | R/W  | General use        |

| R3    | 00011    | R/W  | General use        |

| R4    | 00100    | R/W  | General use        |

| R5    | 00101    | R/W  | General use        |

| R6    | 00110    | R/W  | General use        |

| R7    | 00111    | R/W  | General use        |

| R8    | 01000    | R/W  | General use        |

| R9    | 01001    | R/W  | General use        |

| R10   | 01010    | R/W  | General use        |

| R11   | 01011    | R/W  | General use        |

| R12   | 01100    | R/W  | General use        |

| R13   | 01101    | R/W  | General use        |

| R14   | 01110    | R/W  | General use        |

| R15   | 01111    | R/W  | General use/PARAM0 |

| ACC32 | 10000    | R/W  | General use/result |

| FLAGS | 10001    | R    | Read only          |

R0 – R15 are general purpose registers, ACC32 can be used as a general register but is also used as the destination register for many instructions. FLAGS is a read only register and contains flags useful to the user program. In some instructions more information is required than can fit in the 32-bit instruction field, in these cases R15 is used as an additional parameter register referred to as PARAMO.

ACC64 is the 64-bit accumulator for the 32x32 multiplier.

MREG registers are a bank of 128 32-bit registers called MR0 to MR127 that can be used for additional 32-bit storage. These registers can also be read indirectly by the CPY\_CMX command allowing the registers to be preloaded by the .MREG directive and used as a lookup table.

Delay RAM is a 32Kx16-bit block and is the slowest to access.

Special function registers (SFRs), while not shown in the block diagram, are a collection of registers that provide specific functions or information to a program. Some SFRs are read only while others are write only. For a complete list of SFRs please see the FXCore datasheet or the "Special Function Registers" portion of the "Reserved Words" section later in this document.

## **FLAGS** Register

The FLAGS register contains status flags that may be useful to a user program, this is a 16-bit LSB aligned register so flag values may be easily isolated with an instruction like ANDI.

| Bit | Name     | Meaning                          |

|-----|----------|----------------------------------|

| 15  | OUT3OFLO | Output 3 overflow                |

| 14  | OUT2OFLO | Output 2 overflow                |

| 13  | OUT10FL0 | Output 1 overflow                |

| 12  | OUT00FLO | Output 0 overflow                |

| 11  | IN3OFLO  | Input 3 clip                     |

| 10  | IN2OFLO  | Input 2 clip                     |

| 9   | IN10FLO  | Input 1 clip                     |

| 8   | IN00FLO  | Input 0 clip                     |

| 7   | XXX      | RESERVED                         |

| 6   | XXX      | RESERVED                         |

| 5   | TB2nTB1  | 0: Tap button "1" event          |

|     |          | 1: Tap button "2" event          |

| 4   | TAPSTKY  | TAP sticky event, user has       |

|     |          | pressed the tap button for       |

|     |          | longer than TAPSTKRLD            |

| 3   | NEWTT    | New tap tempo value in           |

|     |          | TAPTEMPO                         |

| 2   | TAPRE    | Tap button release event, user   |

|     |          | stopped pressing the tap button  |

| 1   | TAPPE    | Tap button push event, user      |

|     |          | started pressing the tap button  |

| 0   | TAPDB    | Debounced tap button level, 0 if |

|     |          | pressed and 1 if not pressed     |

Flags are valid for as long as the event occurs (i.e. overflow flags) or for 1 sample period (i.e. new tap value)

## Instruction Format

The instruction is a 32-bit word broken into 3 primary fields:

| 31 30 29 28 27 26 25 | 24 | 23 22 21 20 19 18 17 16 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|----------------------|----|-------------------------|---------------------------------------|

| "I" Field            | 0  | "R" Field               | "M" Field                             |

31:25 - "I" field, instruction field

24 - Reserved, set to 0

23:16 – "R" field, generally a core register.

15:0 – "M" field, may be used to point into delay memory, used to address a second register if required, the 5-bit value for a shift, 16-bit coefficient, etc. LSB aligned field.

For Extended Operations both the R and M fields may be used in a different manner.

## Symbols used in instruction descriptions

| FXCore no                                                                    | otation conventions                                                                               |  |  |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| +                                                                            | Arithmetic addition                                                                               |  |  |

| -                                                                            | Arithmetic subtraction                                                                            |  |  |

| *                                                                            | Arithmetic multiplication                                                                         |  |  |

| /                                                                            | Arithmetic division                                                                               |  |  |

| ~                                                                            | Bit inversion (1's compliment)                                                                    |  |  |

| &                                                                            | Bitwise AND                                                                                       |  |  |

| &&                                                                           | Logical AND                                                                                       |  |  |

|                                                                              | Bitwise OR                                                                                        |  |  |

| П                                                                            | Logical OR                                                                                        |  |  |

| 0                                                                            | Bitwise XOR                                                                                       |  |  |

| {A,B}                                                                        | Concatenation of 2 values to create a larger value, i.e. {0x12, 0x34} results in the value 0x1234 |  |  |

| [X]                                                                          | The value in a register or at a specific memory address. X is a register number or a memory       |  |  |

|                                                                              | address. I.e [CREG0] (value in core reg 0), [FLAGS] (FLAGS sfr)                                   |  |  |

| X                                                                            | Absolute value of X                                                                               |  |  |

| X <sup>Y</sup>                                                               | X raised to the Y power                                                                           |  |  |

| X <sub>b:a</sub>                                                             | Bit range of b to a of value X                                                                    |  |  |

| @REG                                                                         | Indirect addressing, REG is used as a pointer into another memory                                 |  |  |

| @@REG                                                                        | Indirect addressing, REG is used as a pointer into delay memory without adding address counter    |  |  |

| ImmX                                                                         | An immediate integer value of X bits, unsigned                                                    |  |  |

| SImmX                                                                        | An immediate integer value of X bits including a sign bit                                         |  |  |

| S.X                                                                          | An immediate signed fractional value in the range of -1.0 to +0.99 of 1+X bits                    |  |  |

| SX.Y                                                                         | An immediate signed real value with X integer bits and Y fractional bits, total length of         |  |  |

|                                                                              | 1+X+Y bits                                                                                        |  |  |

| CREG                                                                         | Any core register is valid (CREG0-15, ACC32, FLAGS)                                               |  |  |

| CREGNA                                                                       | Only core registers 0 to 15 and ACC32 are valid                                                   |  |  |

| MREG                                                                         | Memory register                                                                                   |  |  |

| MEM                                                                          | Delay memory                                                                                      |  |  |

| SFR                                                                          | Special function register                                                                         |  |  |

| X< <y< td=""><td>Left bit shift of X by the value represented by Y</td></y<> | Left bit shift of X by the value represented by Y                                                 |  |  |

| X>>Y                                                                         | Right bit shift of X by the value represented by Y                                                |  |  |

There is the 64-bit CPU register for 32x32 MAC ops. While in the core it is not considered a core register as it cannot be used directly in most instructions.

The FX Core assembler attempts to resolve values based on the type expected in an instruction, an ADDSI instruction expect a value between -1.0 and +0.999... and will issue an error is the value is outside that range. An ANDI expects an integer value to use as a mask and will take only the integer portion of the value. However there may be times the user needs to load a 32-bit fractional value into a register

but there are no 32-bit load commands as the data field is limited to 16-bits in the instruction word. This can be accomplished by use of the ".I" and ".u" extensions to parameter values. As an example:

// load a 32-bit value into a register, coeff is a 32-bit fractional value, max32 is 0x7FFFFFFF wrdld r3, (coeff\*max32).u // load the upper 16-bits into R3, clear lower 16-bits ori r3 (coeff\*max32).l // load the lower 16-bits so r3 now has the 32-bit fractional coefficient in it

Math Operations

#### FX Core Instruction Set Document Version 1.0 February 2020

## ABS – Absolute value of a core register

Use: ABS CREG ACC32 = |CREG|

C: Core register

Description: The absolute value of the core register. The result is placed in ACC32.

Example: ABS R0

## CLRACC64 - Clear the 64-bit accumulator

Use: CLRACC64 ACC64 = 0

Encoding: 0000 0010 0000 0000 0000 0000 0000

Description: ACC64 is set to 0x00000000

Example: CLRACC64

## ADDI – Add a 16bit signed integer to 32 bit core register, not saturated (modulo $2^{32}$ )

Use: ADDI CREG, SImm16

ACC32 = CREG + {SSSS SSSS SSSS, SImm16}

Encoding: 0000 0100 000C CCCC SIII IIII IIII IIII

C: Core register SI: Signed Imm16

Description: SImm16 is LSB aligned, the sign bit is extended across bits 31:16 prior to the 32-bit add. The

result is placed in ACC32 and is allowed to "roll over".

Example: ADDI RO, -1

## ADD – Unsigned addition of two core registers, not saturated (modulo 2<sup>32</sup>)

Use: ADD CREGX, CREGY ACC32 = CREGX + CREGY

Encoding: 0000 0110 000X XXXX 0000 0000 000Y YYYY

X: Core register X Y: Core register Y

Description: Two core registers are added together. The result is placed in ACC32 and is allowed to "roll

over".

Example: ADD R2, R3

## ADDS – Signed addition of two core registers, saturated

Use: ADDS CREGX, CREGY ACC32 = CREGX + CREGY

Encoding: 0000 1000 000X XXXX 0000 0000 000Y YYYY

X: Core register X Y: Core register Y

Description: Two core registers are added together. The result is placed in ACC32 and is saturated to the

maximum positive (0x7FFFFFFF) or negative (0x80000000) value as appropriate

Example: ADDS ACC32, R0

## ADDSI – Signed addition of 32-bit S.31 core register with 16-bit S.15 (MSB aligned), saturated

Use: ADDS CREG, S.15

$ACC32 = CREG + \{S.15 << 16, 0x0000]\}$

Encoding: 0000 1010 000C CCCC SFFF FFFF FFFF

C: Core register S: Sign bit

F: Fractional bits

Description: Prior to the 32-bit addition, the 16-bit S.15 immediate value is shifted left by 16 bits and zero padded, converting the S.15 immediate value into an S.31 value. The result is placed in ACC32 and is saturated to the maximum positive (0x7FFFFFFF) or negative (0x80000000) S.31 signed fractional value.

Example ADDSI RO, 0.5

## SUB – Unsigned subtraction of two core registers, not saturated (modulo 2<sup>32</sup>)

Use: SUB CREGX, CREGY ACC32 = CREGX - CREGY

Encoding: 0000 1100 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: Unsigned subtraction of two core registers. The result is placed in ACC32 and is allowed to

"roll over".

## SUBS – Signed subtraction of two core registers, saturated

Use: SUBS CREGX, CREGY ACC32 = CREGX - CREGY

Encoding: 0000 1110 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: Signed subtraction of core register Y from core register X. The result is placed in ACC32 and is saturated to the maximum positive (0x7FFFFFFF) or negative (0x80000000) value as appropriate Example SUBS RO, R1

## SL – Shift left logical using an immediate 5-bit value

Use: SL CREG, Imm5

$ACC32 = CREG \ll Imm5, ACC32_0 \ll 0$

Encoding: 0001 0000 000C CCCC 0000 0000 000I IIII

C: Core register

I: Imm5

Description: CREG is shifted left by the number of bit positions specified by the Imm5 value. Zeros are

inserted into the bit positions emptied by the shift. The result is placed in ACC32.

Example: SL RO, 8

## SLR – Shift left logical using the 5-LSBs of a core register

Use: SLR CREGX, CREGY

$ACC32 = CREGX \ll CREGY_{4:0}$ ,  $ACC32_0 \ll 0$

Encoding: 0001 0010 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: CREGX is shifted left by the number of bit positions specified by CREGY<sub>4:0</sub>. Zeros are inserted

into the bit positions emptied by the shift. The result is placed in ACC32.

Example: SLR RO, R1

## SLS – Shift left arithmetic with saturation using an immediate 5-bit value

Use: SLS CREG, Imm5

ACC32 = CREG << Imm5, ACC32<sub>0</sub> <- 0 or saturate to max +/- value Encoding: 0001 0100 000C CCCC 0000 0000 0001 IIII

C: Core register

I: Imm5

Description: CREG is shifted left by the number of bit positions specified by the Imm5 value. Zeros are inserted into the bit positions emptied by the shift. The result is placed in ACC32 and is saturated to the maximum positive (0x7FFFFFFF) or negative (0x80000000) value as appropriate

Example SLS RO, 8

## SLSR – Shift left arithmetic with saturation using the 5-LSBs of a core register

Use: SLSR CREGX, CREGY

ACC32 = CREGX << CREGY<sub>4:0</sub>, ACC32 $_0$  <- 0 or saturate to max +/- value Encoding: 0001 0110 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: CREGX is shifted left by the number of bit positions specified by CREGY<sub>4:0</sub>. Zeros are inserted into the bit positions emptied by the shift. The result is placed in ACC32 and is saturated to the

maximum positive (0x7FFFFFFF) or negative (0x80000000) value as appropriate Example SLSR R0, R1

## SR – Shift right logical using an immediate 5-bit value

Use: SR CREG, Imm5

$ACC32 = CREG >> Imm5, 0 -> ACC32_{31}$

Encoding: 0001 1000 000C CCCC 0000 0000 000I IIII

C: Core register

I: Imm5

Description: CREG is shifted right by the number of bit positions specified by the Imm5 value. Zeros are

inserted into the bit positions emptied by the shift. The result is placed in ACC32

Example: SR RO, 8

## SRR – Shift right logical using the 5-LSBs of a core register

Use: SRR CREGX, CREGY

$ACC32 = CREGX >> CREGY_{4:0}$ , 0 ->  $ACC32_{31}$

Encoding: 0001 1010 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: CREGX is shifted right by the number of bit positions specified by CREGY<sub>4:0</sub>. Zeros are

inserted into the bit positions emptied by the shift. The result is placed in ACC32

Example: SRR RO, R1

## SRA – Shift right arithmetic using an immediate 5-bit value

Use: SRA CREG, Imm5

$ACC32 = CREG >> Imm5, CREG_{31} -> ACC32_{31}$

Encoding: 0001 1100 000C CCCC 0000 0000 000I IIII

C: Core register

I: Imm5

Description: CREG is shifted right by the number of bit positions specified by the Imm5 value. The sign bit of CREG (CREG<sub>31</sub>) is inserted into the bit positions emptied by the shift. The result is placed in ACC32

Example: SRA RO, 8

## SRAR – Shift right arithmetic using the 5-LSBs of a core register

Use: SRAR CREGX, CREGY

$ACC32 = CREGX >> CREGY_{4:0}$ ,  $CREGX_{31} -> ACC32_{31}$

Encoding: 0001 1110 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: CREGX is shifted right by the number of bit positions specified by CREGY<sub>4:0</sub>. The sign bit of CREGX (CREGX<sub>31</sub>) is inserted into the bit positions emptied by the shift. The result is placed in ACC32

Example: SRAR RO, R1

MACRR – Multiply and accumulate using 64-bit accumulator (S.63), 32-bit (S.31) x 32-bit (S.31) multiply with saturation

Use: MACRR CREGX, CREGY ACC64 = ACC64 + CREGX \* CREGY

Encoding: 0010 0000 000X XXXX 0000 0000 000Y YYYY

X: Core register

Y: Core register

appropriate

Example: MACRR RO, R1

MACRI – Multiply and accumulate using 64-bit accumulator (S.63), 32-bit (S.31) x 16-bit (S.15) coefficient multiply

Use: MACRI CREG, S.15

ACC64 = ACC64 + CREG \* {S.15, 0x0000}

Encoding: 0010 0010 000C CCCC SFFF FFFF FFFF FFFF

C: Core register S: Sign bit

F: Fractional bits

Example: MACRI RO, -0.8

MACRD – Multiply and accumulate using 64-bit accumulator (S.63), 32-bit (S.31) x 16-bit (S.15) delay memory multiply

Use: MACRD CREG, ADDRESS

ACC64 = ACC64 + CREG \* {[ADDRESS], 0X0000}

C: Core register A: Address

Example: MACRD R0, 100

MACID – Multiply and accumulate using 64-bit accumulator (S.63), 8-bit (S.7) coefficient multiply x 16-bit (S.15) delay memory

Use: MACID S.7, ADDRESS

$ACC64 = ACC64 + {S.7,0x000000} * {[ADDRESS], 0X0000}$

Encoding: 0010 0110 SFFF FFFF 0AAA AAAA AAAA AAAA

S: Sign bit

F: Fractional bits

A: Address

Example: MACHID 0.5, 111

MACHRR – Multiply and accumulate using 64-bit accumulator (S3.60), 32-bit (S.31) x 32-bit (S.31 shifted to S3.28) multiply

Use: MACHRR CREGX, CREGY

ACC64 = ACC64 + CREGX \* (CREGY >> 3)

Encoding: 0010 1000 000X XXXX 0000 0000 000Y YYYY

X: Core register

Y: Core register

Example: MACHRR R0, ACC32

MACHRI – Multiply and accumulate using 64-bit accumulator (S3.60), 32-bit (S.31)  $\times$  16-bit (S.15 shifted right and zero appended to S3.28) multiply

Use: MACHRI CREG, S.15

$ACC64 = ACC64 + CREG * {(S.15 >> 3), 0x0000}$

Encoding: 0010 1010 000C CCCC SFFF FFFF FFFF FFFF

C: Core register S: Sign bit

F: Fractional bits

Example: MACHRI RO, -0.8

MACHRD – Multiply and accumulate using 64-bit accumulator (S3.60), 32-bit (S.31) x 16-bit (S.15 shifted right to S3.15 and zero appended to S3.28) delay memory

Use: MACHRD CREG, ADDRESS

ACC64 = ACC64 + CREG \* {[ADDRESS]>>3, 0x0000}

C: Core register

A: Address

Example: MACHRD R0, 100

MACHID – Multiply and accumulate using 64-bit accumulator (S3.60), 8-bit (S.7 zero appended to S.32) coefficient x 16-bit (S.15 shifted right to S3.15 and zero appended to S3.28) delay memory multiply

Use: MACID S.7, ADDRESS

ACC64 = ACC64 + {S.7, 0x000000} \* {[ADDRESS]>>3, 0x0000}

Encoding: 0010 1110 SFFF FFFF 0AAA AAAA AAAA AAAA

S: Sign bit

F: Fractional bits

A: Address

Example: MACHID -0.8, 100

MULTRR – Saturated multiply of two core registers, 32-bit (S.31) x 32-bit (S.31), 32 MSBs of the 64-bit product in ACC32

Use: MULTRR CREGX, CREGY ACC32 = (CREGX \* CREGY)<sub>63:32</sub>

Encoding: 0011 0000 000X XXXX 0000 0000 000Y YYYY

X: Core register

Y: Core register

Description: CREGX is multiplied by CREGY and the 32 MSBs are placed in ACC32. If both CREGX and

CREGY are -1.0 the result will be saturated to the maximum positive (0x7FFFFFFF) value

Example: MULTRR RO, R1

#### MULTRI – Multiply to 32-bit accumulator (S.31), 32-bit (S.31) x 16-bit (S.15) multiply

Use: MULTRI CREG, S.15

$ACC32 = (CREG * {S.15, 0x0000})_{63:32}$

Encoding: 0011 0010 000C CCCC SFFF FFFF FFFF FFFF

C: Core register S: Sign bit

F: Fractional bits

Description: CREG is multiplied by the S.15 coefficient zero padded to 32-bits and the 32 MSBs are placed in ACC32. If both CREGX and the S.15 coefficient are -1.0 the result will be saturated to the maximum positive (0x7FFFFFFF) value

Example: MULTRI R0, -0.9

## NEG – Negate a core register, 2's complement saturated

Use: NEG CREG ACC32 = -CREG

C: Core register

Description: The 2's complement of CREG is placed in ACC32. If CREGNE is -1.0 the result will be

saturated to the maximum positive (0x7FFFFFF) value

Example: NEG RO

## LOG2 – Calculate the log base 2 of the absolute value of a register

Use: LOG2 CREG

$ACC32 = LOG_2(|CREG|)$

C: Core register

Description: The  $\log_2$  of the absolute value in CREG is placed in ACC32, the result is in an S5.26 format

where S is the sign followed by the 5 bit integer and 26 bit fraction.

Example: LOG2 RO

## EXP2 – Calculate 2<sup>^</sup> value of a register

Use: EXP2 CREG ACC32 =  $2^{CREG}$

C: Core register

Description: 2 is raised to the power in CREG then placed in ACC32, the number format in the CREG

must be S5.26 and S must be 1 indicating a negative number.

Example: EXP2 R0

**Copy Operations**

## CPY CC – Copy from one core register to another

Use: CPY CC CREGNAX, CREGY

CREGNAX = CREGY

Encoding: 0110 0000 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: CREGY is copied to CREGNAX

Example: CPY\_CC RO, FLAGS

## CPY\_CM – Copy from MREG register to core register

Use: CPY\_CM CREGNA, MREG

CREGNA = MREG

Encoding: 0110 0010 000C CCCC 0000 0000 0MMM MMMM

C: Core register M: MREG register

Description: MREG is copied to CREGNA

Example: CPY\_CM R0, MR64

## CPY CS – Copy from special function register (SFR) to core register

Use: CPY\_CS CREGNA, SFR

CREGNA = SFR

Encoding: 0110 0100 000C CCCC 0000 0000 00SS SSSS

C: Core register S: SFR register

Description: SFR is copied to CREGNA. Note that some SFRs are 16 bit and may be MSB or LSB aligned or may be write only and not readable (i.e. OUT0) please see the "Special Function Registers" section for

further information. Example: CPY\_CS RO, INO

## CPY MC – Copy from core register to MREG register

Use: CPY\_MC MREG, CREG

MREG = CREG

Encoding: 0110 0110 000C CCCC 0000 0000 0MMM MMMMM

C: Core register M: MREG register

Description: CREG is copied to MREG Example: CPY MC MR17, FLAGS

## CPY\_SC – Copy from core register to special function register (SFR)

Use: CPY SC SFR, CREG

SFR = CREG

Encoding: 0110 1000 000C CCCC 0000 0000 00SS SSSS

C: Core register S: SFR register

Description: CREG is copied to SFR. Note that some SFRs are not 32-bit and may be MSB or LSB aligned or may be read only and not writeable (i.e. INO) please see the "Special Function Registers" section for further information.

Example: CPY\_SC OUTO, RO

# CPY\_CMX – Copy from MREG register to core register using a second core register as the index register to address the MREG

Use: CPY\_CMX CREGNAX, CREGY CREGNAX = MREG(@CREGY<sub>6:0</sub>)

Encoding: 0110 1010 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: CREGY<sub>6:0</sub> are used to address which MREG register to read. This allows the MREG registers

to be used as a look up table if they were initialized to values using .MREG directives

Example: CPY\_CMX R0, R1

Load/store Operations

## RDACC64U – Copy the upper 32-bits from the 64-bit accumulator to a core register

Use: RDACC64U CREGNA CREGNA = ACC64<sub>63:32</sub>

C: Core register

Description: ACC64<sub>63:32</sub> is copied to CREGNA

Example: RDACC64U R0

## RDACC64L - Copy the lower 32-bits from the 64-bit accumulator to a core register

Use: RDACC64L CREGNA CREGNA = ACC64<sub>31:0</sub>

C: Core register

Description: ACC64<sub>31:0</sub> is copied to CREGNA

Example: RDACC64L RO

## LDACC64U – Load the upper 32-bits of the 64-bit accumulator from a core register

Use: LDACC64U CREG ACC64<sub>63:32</sub> = CREG

C: Core register

Description: CREG is copied to ACC64<sub>63:32</sub>

Example: LDACC64U R0

## LDACC64L – Load the lower 32-bits of the 64-bit accumulator from a core register

Use: LDACC64L CREG ACC64<sub>31:0</sub> = CREG

C: Core register

Description: CREG is copied to ACC64<sub>31:0</sub>

Example: LDACC64L RO

## RDDEL – Read from delay memory into a core register using an immediate address

Use: RDDEL CREGNA, ADDRESS CREGNA = {[Address], 0x0000}

C: Core register

A: Address

Description: The data at ADDRESS is zero appended and placed in CREGNA

Example: RDDEL RO, 200

WRDEL – Write to delay memory from a core register using an immediate address

Use: WRDEL ADDRESS, CREG

[ADDRESS] =  $CREG_{31:16}$

C: Core register A: Address

Description: CREG<sub>31:16</sub> is written to ADDRESS.

Example: WRDEL R0, 200

RDDELX – Read from delay memory into a core register using a second core register as the index register to address the delay memory

Use: RDDELX CREGNAX, CREGY CREGNAX = {[@CREGY<sub>14:0</sub>], 0x0000}

Encoding: 1000 1100 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: CREGY<sub>14:0</sub> are used as the address into delay memory. The data at this address is zero

appended and placed in CREGNAX Example: RDDELX RO, ACC32

WRDELX – Write the value in a core register to delay memory using a second core register as the index register to address the delay memory

Use: WRDELX CREGX, CREGY @CREGX<sub>14:0</sub> = CREGY<sub>31:16</sub>

Encoding: 1000 1110 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description:  $CREGX_{14:0}$  are used as the address into delay memory.  $CREGY_{31:16}$  are written to this address.

Example: WRDELX R0, ACC32

RDDIRX – Read from delay memory into a core register using a second core register as the index register to address the delay memory without adding address counter

Use: RDDIRX CREGNAX, CREGY

$CREGNAX = \{ [@@CREGY_{14:0}], 0x0000 \}$

Encoding: 1001 0000 000X XXXX 0000 0000 000Y YYYY

X: Core register

Y: Core register

Description: CREGY<sub>14:0</sub> are used as the absolute address into delay memory, the address counter is not

added to this address. The data at this address is zero appended and placed in CREGNAX

Example: RDDIRX RO, ACC32

WRDIRX – Write the value in a core register to delay memory using a second core register as the index register to address the delay memory without adding address counter

Use: WRDIRX CREGX, CREGY @@CREGX<sub>14:0</sub> = CREGY<sub>31:16</sub>

Encoding: 1001 0010 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: CREGX<sub>14:0</sub> are used as the address into delay memory, the address counter is not added to

this address. CREGY<sub>31:16</sub> are written to this address.

Example: WRDIRX R0, ACC32

SAT64 – Copy the 32 MSBs from ACC64 (S3.60), shift left 3 bits and saturate to an S.31 format and place into core register

Use: SAT64 CREGNA

CREGNA =  $ACC64_{63:32} << 3$  with saturation

C: Core register

Description: ACC64 $_{63:32}$  are shifted left 3 bit to remove the headroom added by instructions like MACHRR. The result is placed in CREGNA and is saturated to the maximum positive (0x7FFFFFFF) or

negative (0x8000000) value as appropriate

Example: SAT64 R0

WRDLD – Load a 16-bit immediate value to the upper 16-bits of a core register, 0s to LSBs

Use: WRDLD CREGNA, Imm16 CREGNA = {Imm16, 0x0000}

C: Core register

I: 16-bit immediate value

Description: The 16-bit immediate value is 0 appended and placed in CREGNA. Note that a WRDLD instruction immediately followed by an ORI instruction can be used to load a 32-bit immediate value

into ACC32

Example: WRDLD 0x4711

Logic Operations

#### FX Core Instruction Set Document Version 1.0 February 2020

## INV – Invert (1's comp) core register

Use: INV CREG

ACC32 = ~CREG

C: Core register

Description: Every bit in CREG is inverted (1's comp) and the result is placed in ACC32

Example: INV R0

## OR - Bitwise OR of 2 core registers to ACC32

Use: OR CREGX, CREGY ACC32 = CREGX | CREGY

Encoding: 1010 0010 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: CREGX and CREGY are ORed together and the result is placed in ACC32

Example: OR RO, R1

## ORI – Bitwise OR of core register with a 16-bit immediate value 0 extended to ACC32

Use: ORI CREG, Imm16

$ACC32 = CREG \mid \{0x0000, Imm16\}$

C: Source/destination core register

I: 16-bit immediate value

Description: The Imm16 value is 0 extended and ORed with CREG and the result is placed in ACC32. Note that a WRDLD instruction immediately followed by an ORI instruction can be used to load a 32-bit

immediate value into ACC32 Example: ORI RO, 0x4711

#### AND – Bitwise AND of 2 core registers to ACC32

Use: AND CREGX, CREGY ACC32 = CREGX & CREGY

Encoding: 1010 0110 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: CREGX and CREGY are ANDed together and the result is placed in ACC32

Example: AND RO, R1

## ANDI – Bitwise AND of core register with a 16-bit immediate value 0 extended to ACC32

Use: ANDI CREG, Imm16

ACC32 = REGD & {0x0000, Imm16}

C: Core register

I: 16-bit immediate value

Description: The Imm16 value is 0 extended and ANDed with CREG and the result is placed in ACC32.

Example: ANDI FLAGS, 0x0100

## XOR – Bitwise XOR of 2 core registers to ACC32

Use: XOR CREGX, CREGY ACC32 = CREGX ⊕ CREGY

Encoding: 1010 1010 000X XXXX 0000 0000 000Y YYYY

X: Core register Y: Core register

Description: CREGX and CREGY are XORed together and the result is placed in ACC32

Example: XOR R0, ACC32

## XORI – Bitwise XOR of core register with a 16-bit immediate value 0 extended to ACC32

Use: XORI CREG, Imm16

$ACC32 = CREG \oplus [0x0000, Imm16]$

C: Core register

I: 16-bit immediate value

Description: The Imm16 value is 0 extended and XORed with CREG and the result is placed in ACC32.

Example: ANDI FLAGS, 0x0100

#### JGEZ – Jump if core register value is >= 0

Use: JGEZ CREG, OFFSET

If (CREG >= 0) PC = PC + OFFSET

Encoding: 1010 1110 000C CCCC 0000 0000 0000

C: Core register

o: Offset added to address counter, positive only

Description: If CREG is greater than or equal to zero then the offset is added to the current program counter (PC). OFFSET is always positive no back jumping allowed. Current PC + OFFSET must not exceed the address of the last instruction within the FXCore program.

Example: JGEZ RO, Vader

## JNEG – Jump if core register value is < 0

Use: JNEG CREG, OFFSET

If (CREG < 0) PC = PC + OFFSET

Encoding: 1011 0000 000C CCCC 0000 0000 0000

C: Core register

o: Offset added to address counter, positive only

Description: If CREG is less than zero then the offset is added to the current program counter (PC).

${\sf OFFSET}\ is\ always\ positive\ no\ back\ jumping\ allowed.\ Current\ PC+OFFSET\ must\ not\ exceed\ the\ address\ of\ property and the property of\ property of\ property of\ property.$

the last instruction within the FXCore program.

Example: JNEG R0, Yoda

## JNZ – Jump if core register value is != 0

Use: JNZ CREG, OFFSET

If (CREG!= 0) PC = PC + OFFSET

Encoding: 1011 0010 000C CCCC 0000 0000 0000

C: Core register

o: Offset added to address counter, positive only

Description: If CREG is not equal to zero then the offset is added to the current program counter (PC).

OFFSET is always positive no back jumping allowed. Current PC + OFFSET must not exceed the address of

the last instruction within the FXCore program.

Example: JNZ RO, Luke

#### JZ - Jump if core register value = 0

Use: JZ CREG, OFFSET

If (CREG == 0) PC = PC + OFFSET

Encoding: 1011 0100 000C CCCC 0000 0000 0000

C: Core register

o: Offset added to address counter, always positive no back jumping allowed

Description: If CREG is equal to zero then the offset is added to the current program counter (PC).

OFFSET is always positive no back jumping allowed. Current PC + OFFSET must not exceed the address of the last instruction within the FXCore program.

Example: JZ RO, Leia

## JZC – Jump if core register value is different sign from acc32

Use: JZC CREG, OFFSET

If (SGN(CREG) != SGN(ACC32)) PC = PC + OFFSET

Encoding: 1011 0110 000C CCCC 0000 0000 0000

C: Core register

o: Offset added to address counter, positive only

Description: If the sign of CREG is not equal to the sign of ACC32 then the offset is added to the current

program counter (PC). OFFSET is always positive no back jumping allowed. Current PC + OFFSET must not exceed the address of the last instruction within the FXCore program.

Example: JZ RO, Chewbacca

## JMP – Jump always

Use: JMP OFFSET PC = PC + OFFSET

Encoding: 1011 1000 0000 0000 0000 0000 0000

o: Offset added to address counter, positive only

Description: OFFSET is added to the current program counter (PC). OFFSET is always positive no back jumping allowed. Current PC + OFFSET must not exceed the address of the last instruction within the

FXCore program.

Example: JMP, ObiWan

**Extended Operations**

#### APA – First instruction for all-pass filter with fixed values

Use: APA S.7, ADDRESS

ACC32 = [ADDRESS]\*S.7 +ACC32, R15=[ADDRESS]

Encoding: 1100 0000 SFFF FFFF 0AAA AAAA AAAA AAAA

S: Sign Bit

F: Fractional bits

A: Address of tail of all-pass delay block

Description: ACC32 holds the input to the all-pass and will be over written, R15 (PARAMO) will be overwritten with the tail of the all-pass delay block. APA and APB should be used as a pair to create the all-pass. Note that the coefficient in APA should be the inverse (2's comp) of the coefficient in APB, i.e. if APB is a positive coefficient then APA should be negative

Example: APA -0.4, 200

## APB – Second instruction for all-pass filter with fixed values

Use: APB S.7, ADDRESS

[ADDRESS] = ACC32, ACC32 = (ACC32 \* S.7) + R15

Encoding: 1100 0010 SFFF FFFF 0AAA AAAA AAAA AAAA

S: Sign Bit

F: Fractional bits

A: Address of head of all-pass delay block

Description: R15 (PARAMO) must have the tail of the all-pass delay block from the preceding APA, ACC32 will hold the result of the all-pass. APA and APB should be used as a pair to create the all-pass. Note that the coefficient in APB should be the inverse (2's comp) of the coefficient in APA, i.e. if APA is a negative coefficient then APB should be positive

Example: APB 0.4, 0

## APRA – First instruction for all-pass filter using register for coefficient value

Use: APRA CREGN, ADDRESS

ACC32 = [ADDRESS]\*-CREGN + ACC32, R15=[ADDRESS]

C: Core register

A: Address of tail of all-pass delay block

Description: ACC32 holds the input to the all-pass and will be over written, R15 (PARAMO) will be overwritten with the tail of the all-pass delay block. APRA and APRB should be used as a pair to create the all-pass. Note that APRA will multiply the memory value read from the tail of the all-pass delay block with the 2's complement of the all-pass coefficient within CREGN

Example: APRA RO, 200

## APRB – Second instruction for all-pass filter using register for coefficient value

Use: APRB CREGN, ADDRESS

[ADDRESS] = ACC32, ACC32 = (ACC32\* CREGN) + R15

C: Core register

A: Address of head of all-pass delay block

Description: R15 (PARAMO) must have the tail of the all-pass delay block from the preceding APRA, ACC32 will hold the result of the all-pass. APRA and APRB should be used as a pair to create the all-pass

Example: APRB R0, 0

## APRRA – First instruction for all-pass filter using register for both values

Use: APRRA CREGNX, CREGNY

$ACC32 = @CREGNY_{14:0}*-CREGNX + ACC32, R15=[CREGNY_{14:0}]$

Encoding: 1100 1000 000X XXXX 0000 0000 000Y YYYY

X: Register that holds the all-pass coefficient

Y: Register that holds the address of tail of all-pass delay block

Description: ACC32 holds the input and will be over written, R15 (PARAMO) will be overwritten with the tail of the all-pass delay block. APRRA and APRRB should be used as a pair to create the all-pass. Note that APRRA will multiply the memory value read from the tail of the all-pass delay block with the 2's complement of the all-pass coefficient within CREGNX

Example: APRRA RO, R1

## APRRB – Second instruction for all-pass filter using register for both values

Use: APRRB CREGNX, CREGNY

$@CREGNY_{14:0} = ACC32, ACC32 = (ACC32* CREGNX) + R15$

Encoding: 1100 1010 000X XXXX 0000 0000 000Y YYYY

X: Register that holds the all-pass coefficient

Y: Register that holds address of head of all-pass delay block

Description: R15 (PARAMO) should have the tail of the all-pass delay block from APRRA, ACC32 will hold

the result of the all-pass. APRRA and APRRB should be used as a pair to create the all-pass

Example: APRRB RO, R1

## APMA – First instruction for all-pass filter using MREG for delay

Use: APMA CREGN, MREG

ACC32 = MREG\*-CREGN + ACC32, R15=MREG

Encoding: 1100 1100 000C CCCC 0000 0000 0MMM MMMM

C: Register that holds the all-pass coefficient

M: MREG that holds single delay

Description: APMA is part of a pair of instructions to perform an all-pass on a single delay element located in an MREG, this is useful for a phaser or other single delay AP. ACC32 holds the input and will

be over written, R15 (PARAMO) will be overwritten with value in the MREG. APMA and APMB should be used as a pair to create the all-pass. Note that APMA will multiply the value read from the all-pass delay register MREG with the 2's complement of the all-pass coefficient within CREGN

Example: APMA RO, MR10

#### APMB – Second instruction for all-pass filter using MREG for delay

Use: APMB CREGN, MREG

MREG = ACC32, ACC32 = (ACC32\* CREGN) + R15

Encoding: 1100 1110 000C CCCC 0000 0000 0MMM MMMM

C: Register that holds the all-pass coefficient

M: MREG that holds single delay

Description: R15 (PARAMO) should have value from MREG from APMA, ACC32 will hold the result of the

all-pass. APMA and APMB should be used as a pair to create the all-pass

Example: APMB R0, MR10

#### CHR – Chorus on delay mem

Use: CHR LFO | W | N, ADDRESS

R15<sub>30:16</sub> = Depth in sample set by user, R15<sub>31</sub> must be 0, ACC32 = Chorus result

Encoding: 1101 0000 0000 NLLW OAAA AAAA AAAA AAAA

N: 0 – use positive SIN or COS, 1 – use negative SIN or COS

LFO: LFO to use W: SIN (0) or COS (1)

A: Address of head of delay block

Description: This instruction will execute a chorus on the delay block starting at ADDRESS using the LFO and phase as defined in the instruction.  $R15_{30:16}$  (PARAMO) must contain the maximum depth in number of samples that the chorus will go into the delay and must be less than the length of the delay,  $R15_{31}$  must be 0.

Example: CHR LFO0|SIN, ChorusDelay

#### PITCH – Pitch shift on delay mem

Use: PITCH RAMP | LENGTH | XFADE, ADDRESS

ACC32 = Pitch result

Encoding: 1101 0010 00XX LLOR 0AAA AAAA AAAA AAAA

X: Crossfade shape to use

L: Block length, 512 (00), 1024 (01), 2048 (10) or 4096 (11)

R: Ramp to use.

A: Address of head of delay block

Description: This instruction will execute a pitch shift through a defined block in delay memory. Please

see the application note "Pitch Shifting in FXCore" for details.

Example: PITCH RMP0 | L2048 | XF0, Pdelay

#### SET – Set a user bit high or low using the selected bit of a register

Use: SET USERBIT | N, CREG

USERBIT = CREG<sub>N</sub>

Encoding: 1101 0100 000C CCCC 0000 0000 00UN NNNN

C: Core register

U: User bit number

N: Bit number within a core register

Description: Bit N of CREG will be written to either USER0 or USER1 pin as determined by USERBIT

Example: SET USER0 | 15, R0

#### INTERP – Do a linear interpolation between two samples in a delay line

Use: INTERP CREG, ADDRESS

$ACC32 = ([@CREG_{30:16} + ADDRESS + 1] - [@CREG_{30:16} + ADDRESS]) * (CREG_{15:0} << 15) + [@CREG_{30:16} + ADDRESS] * (CREG_{15:0} << 15) + [@CREG_{15:0} + ADDRESS] * (CREG_{15:0} + ADDRESS] * (CREG_{15$

ADDRESS]

C: Core register A: Base address

Description: Linear interpolation using (CREG<sub>30:16</sub> + ADDRESS) as the address of the first sample, (CREG<sub>30:16</sub> + ADDRESS + 1) as the address of the second sample and CREG<sub>15:0</sub> as the interpolation coefficient. CREG<sub>15:0</sub> is treated as an unsigned fractional number and a sign bit of "0" is prepended to it. Please see the application note "Using INTERP in FXCore" for details.

Example: INTERP RO, 200

## Reserved Words

The follow are the words reserved in the assembler.

#### Core Registers

R0 through R15 – 32-bit general purpose register

ACC32 – 32-bit accumulator, not settable by .creg, cleared to 0 on program change

FLAGS – Flag register, read only, may not be used as a destination register

## Non-core CPU Registers

ACC64 – 64-bit accumulator S.63 or S3.60 format, only available to 64-bit MAC instructions, not cleared on program change

## **SRAM Based Registers**

MR0 through MR127 – 32-bit SRAM based registers

## **Special Function Registers**

Write values less than 32-bits in size are LSB aligned. "Settable" indicates if the value of the register can be set in the program header using a ".SREG" directive

| Name      | Address | Description                            | Bits    | Read/Write | Settable |

|-----------|---------|----------------------------------------|---------|------------|----------|

| IN0       | 0       | ADC input 0                            | 32      | R          | N        |

| IN1       | 1       | ADC input 1                            | 32      | R          | N        |

| IN2       | 2       | ADC input 2                            | 32      | R          | N        |

| IN3       | 3       | ADC input 3                            | 32      | R          | N        |

| OUT0      | 4       | DAC output 0                           | 32      | W          | Ν        |

| OUT1      | 5       | DAC output 1                           | 32      | W          | N        |

| OUT2      | 6       | DAC output 2                           | 32      | W          | N        |

| OUT3      | 7       | DAC output 3                           | 32      | W          | Ν        |

| PIN       | 8       | Raw user input values                  | 16 LSBs | R          | Ν        |

| SWITCH    | 9       | Debounced user inputs                  | 16 LSBs | R          | Ν        |

| POTO_K    | 10      | POTO smoothing coefficient             | 5 LSBs  | R/W        | Υ        |

| POT1_K    | 11      | POT1 smoothing coefficient             | 5 LSBs  | R/W        | Υ        |

| POT2_K    | 12      | POT2 smoothing coefficient             | 5 LSBs  | R/W        | Υ        |

| POT3_K    | 13      | POT3 smoothing coefficient             | 5 LSBs  | R/W        | Υ        |

| POT4_K    | 14      | POT4 smoothing coefficient             | 5 LSBs  | R/W        | Υ        |

| POT5_K    | 15      | POT5 smoothing coefficient             | 5 LSBs  | R/W        | Υ        |

| РОТО      | 16      | Raw POTO value, S.12 format S always 0 | 13 MSBs | R          | N        |

| POT1      | 17      | Raw POT1 value, S.12 format S always 0 | 13 MSBs | R          | N        |

| POT2      | 18      | Raw POT2 value, S.12 format S always 0 | 13 MSBs | R          | Ν        |

| POT3      | 19      | Raw POT3 value, S.12 format S always 0 | 13 MSBs | R          | N        |

| POT4      | 20      | Raw POT4 value, S.12 format S always 0 | 13 MSBs | R          | N        |

| POT5      | 21      | Raw POT5 value, S.12 format S always 0 | 13 MSBs | R          | N        |

| POT0_SMTH | 22      | Smoothed POTO value, S.31 S always 0   | 32      | R          | Ν        |

| POT1_SMTH | 23      | Smoothed POT1 value, S.31 S always 0   | 32      | R          | Ν        |

| POT2_SMTH | 24      | Smoothed POT2 value, S.31 S always 0   | 32      | R          | Ν        |

| POT3_SMTH | 25      | Smoothed POT3 value, S.31 S always 0   | 32      | R          | N        |

| POT4_SMTH | 26      | Smoothed POT4 value, S.31 S always 0   | 32      | R          | N        |

| POT5_SMTH | 27      | Smoothed POT5 value, S.31 S always 0   | 32      | R          | N        |

| LFO0_F         28         LFO0 frequency coefficient         32         R/W         Y           LFO1_F         29         LFO1 frequency coefficient         32         R/W         Y           LFO2_F         30         LFO2 frequency coefficient         32         R/W         Y           LFO3_F         31         LFO3 frequency coefficient         32         R/W         Y           RAMP0_F         32         RAMP0 frequency coefficient         32         R/W         Y           RAMP1_F         33         RAMP1 frequency coefficient         32         R/W         Y           LFO0_S         34         LFO0 SINE output         32         R         N           LFO0_C         35         LFO0 COSINE output         32         R         N           LFO1_S         36         LFO1 SINE output         32         R         N           LFO2_S         38         LFO2 SINE output         32         R         N           LFO3_S         40         LFO3 SINE output         32         R         N           LFO3_S         40         LFO3 COSINE output         32         R         N           LFO3_C         41         LFO3 COSINE output         32<                                                                                                                                                                                    |                        |    |                                         |    |     |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----|-----------------------------------------|----|-----|---|

| LFO2_F         30         LFO2 frequency coefficient         32         R/W         Y           LFO3_F         31         LFO3 frequency coefficient         32         R/W         Y           RAMP0_F         32         RAMP0 frequency coefficient         32         R/W         Y           RAMP1_F         33         RAMP1 frequency coefficient         32         R/W         Y           LFO0_S         34         LFO0 SINE output         32         R         N           LFO0_C         35         LFO0 COSINE output         32         R         N           LFO1_S         36         LFO1 SINE output         32         R         N           LFO2_C         37         LFO1 COSINE output         32         R         N           LFO2_S         38         LFO2 SINE output         32         R         N           LFO3_S         40         LFO3 SINE output         32         R         N           LFO3_S         40         LFO3 SINE output         32         R         N           LFO3_C         41         LFO3 COSINE output         32         R         N           RAMP0_R         42         RAMP0 output         32         R                                                                                                                                                                                                      | LFO0_F                 | 28 | LFO0 frequency coefficient              | 32 | R/W | Υ |

| LFO3_F         31         LFO3 frequency coefficient         32         R/W         Y           RAMP0_F         32         RAMP0 frequency coefficient         32         R/W         Y           RAMP1_F         33         RAMP1 frequency coefficient         32         R/W         Y           LFO0_S         34         LFO0 SINE output         32         R         N           LFO0_C         35         LFO0 COSINE output         32         R         N           LFO1_S         36         LFO1 SINE output         32         R         N           LFO1_C         37         LFO1 COSINE output         32         R         N           LFO2_S         38         LFO2 SINE output         32         R         N           LFO3_S         40         LFO3 SINE output         32         R         N           LFO3_C         39         LFO3 COSINE output         32         R         N           LFO3_C         41         LFO3 SINE output         32         R         N           RAMP0_R         42         RAMP0 output         32         R         N           RAMP1_R         43         RAMP1 output         32         R         N                                                                                                                                                                                                           | LFO1_F                 | 29 | LFO1 frequency coefficient 32 R/W       |    | R/W | Υ |

| RAMP0_F         32         RAMP0 frequency coefficient         32         R/W         Y           RAMP1_F         33         RAMP1 frequency coefficient         32         R/W         Y           LFO0_S         34         LFO0 SINE output         32         R         N           LFO0_C         35         LFO0 COSINE output         32         R         N           LFO1_S         36         LFO1 SINE output         32         R         N           LFO1_C         37         LFO1 COSINE output         32         R         N           LFO2_C         38         LFO2 SINE output         32         R         N           LFO3_S         40         LFO3 SINE output         32         R         N           LFO3_S         40         LFO3 SINE output         32         R         N           LFO3_C         39         LFO2 COSINE output         32         R         N           LFO3_C         41         LFO3 COSINE output         32         R         N           RAMP0_R         42         RAMP0 output         32         R         N           RAMP1_R         43         RAMP1 output         32         R         N                                                                                                                                                                                                                     | LFO2_F                 | 30 | LFO2 frequency coefficient 32 R/W       |    | Υ   |   |

| RAMP1 F         33         RAMP1 frequency coefficient         32         R/W         Y           LFO0_S         34         LFO0 SINE output         32         R         N           LFO0_C         35         LFO0 COSINE output         32         R         N           LFO1_S         36         LFO1 SINE output         32         R         N           LFO1_C         37         LFO1 COSINE output         32         R         N           LFO2_S         38         LFO2 SINE output         32         R         N           LFO2_S         38         LFO2 COSINE output         32         R         N           LFO3_S         40         LFO3 SINE output         32         R         N           LFO3_C         41         LFO3 COSINE output         32         R         N           RAMP0_R         42         RAMP0 output         32         R         N           RAMP1_R         43         RAMP1 output         32         R         N           MAXTEMPO         44         Maximum number of samples allowed between two tap button presses         32         R         N           TAPTEMPO         45         Latest measured tap tempo time         32<                                                                                                                                                                                    | LFO3_F                 | 31 | LFO3 frequency coefficient              | 32 | R/W | Υ |

| LFOO_S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RAMP0_F                | 32 | RAMPO frequency coefficient             | 32 | R/W | Υ |

| LFO0_C   35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RAMP1_F                | 33 | RAMP1 frequency coefficient             | 32 | R/W | Υ |

| LFO1_S   36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LFO0_S                 | 34 | LFO0 SINE output                        | 32 | R   | N |